The real interest in random generation was started by Galton (if it matters Romans did toss coins and stored bits), random numbers by Pearson, first PRNG is attributed to von Neuman, first working one to Lehmer, as for Fibonacci his insights are nice, but he started his sequences to count rabbits with no connection to PRNG whatsoever. What is an LFSR First: what is a shift register Its a type of electronic logic circuit that stores and transmits data by moving one bit in a particular direction of a register at every step: a basic type of computer memory. The same stands for LFG - lagged Fibonacci generator was (in multiplicative form) introduced by Marsaglia to overcome deffects of additive one. I cannot find any reference why it is called Fibonacci LFSR, but it is inventors will to name it.

pipelining Configurable pipeline registers for use with automated retiming during synthesis. Core Packages These packages provide core functionality that is of general use in a wide array of applications. The name come (afair) from Fibonacci work on recurence relation, his sequence, and further interest in characteristic polynomials of generating sequences, but the one who gave closed form solution to Fibonacci numbers and researched characteristic equation (the one used in generator with possibly minimal monic to make longest period), was Lucas. The following is a summary of the packages provided in VHDL-extras. Its output depends on state and polynomial, not two states.

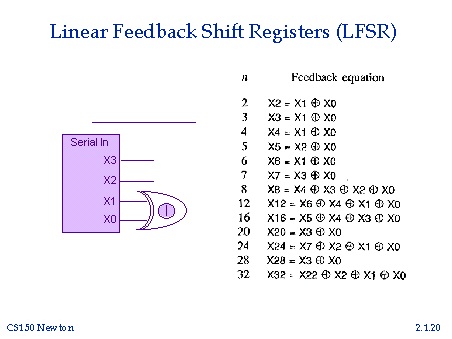

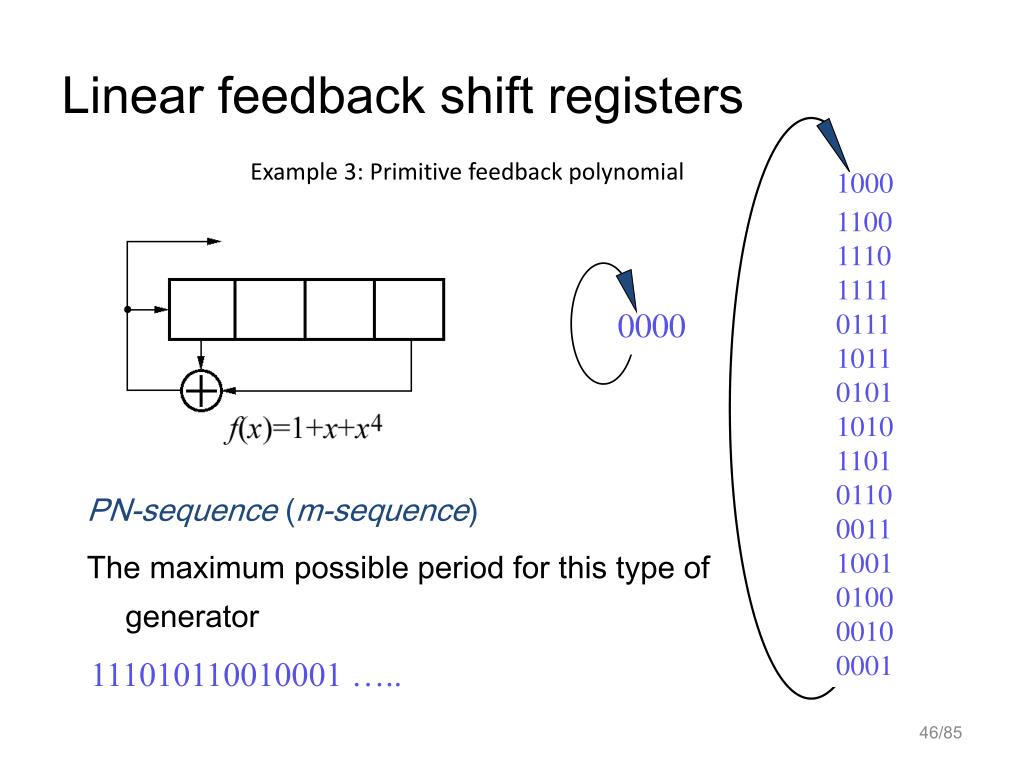

"In computing, a linear-feedback shift register (LFSR) is a shift register whose input bit is a linear function of its previous state." wiki quote. crc := init_crc ( xor_in ) for i in data 'range loop crc := next_crc ( crc, poly, reflect_in, data ( i )) end loop crc := end_crc ( crc, reflect_out, xor_out ) - Implement CRC-16 with nibble-wide inputs: subtype nibble is bit_vector ( 3 downto 0 ) type nibble_vec is array ( natural range ) of nibble variable data : nibble_vec ( 0 to 9 ) variable crc : bit_vector ( poly 'range ). CRC-16-USB constant poly : bit_vector := X"8005" constant xor_in : bit_vector := X"FFFF" constant xor_out : bit_vector := X"FFFF" constant reflect_in : boolean := true constant reflect_out : boolean := true - Implement CRC-16 with byte-wide inputs: subtype word is bit_vector ( 7 downto 0 ) type word_vec is array ( natural range ) of word variable data : word_vec ( 0 to 9 ) variable crc : bit_vector ( poly 'range ).

0 kommentar(er)

0 kommentar(er)